Eidgenössische Technische Hochschule Zürich Institut für Informatik

Niklaus Wirth

The use of MODULA

and

Design and Implementation of MODULA

# THE USE OF MODULA

N.Wirth

### Abstract

Three sample programs are developed and explained with the purpose to demonstrate the use of the programming language Modula. The examples concentrate on the uses of modules, concurrent processes, and synchronizing signals. In particular, they all focus on the problems of operating peripheral devices. The concurrency of their driver processes has to occur in real time. The devices include a typewriter, a card reader, a line printer, a disk, a terminal with tape cassettes, and a graphical display unit. The three programs are listed in full.

Author's address:

Institut für Informatik, ETH, CH-8092 Zürich

### THE USE OF MODULA

# 1. INTRODUCTION

The purpose of this paper is to describe three sample programs written in the programming language Modula, thereby to demonstrate techniques of multiprogramming, and to display the language's flexibility. These examples are by no means parts of "real" systems: on the contrary, the posed problems are constructed to condense typical multiprocessing problems into a nutshell, and in particular to demonstrate the use of Modula's facilities to operate a computer's various devices. The first program uses four devices concurrently: a typewriter keyboard and printer, a card reader, and a line printer. The second program transfers files from a terminal with cassette tapes to a disk store and vice-versa, and the third program operates a graphical display unit.

### 2. THE PROGRAM "DATASTREAMS"

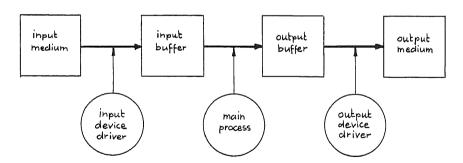

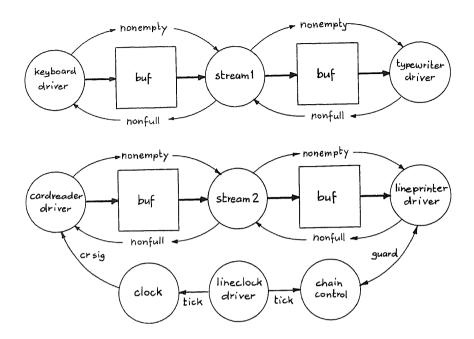

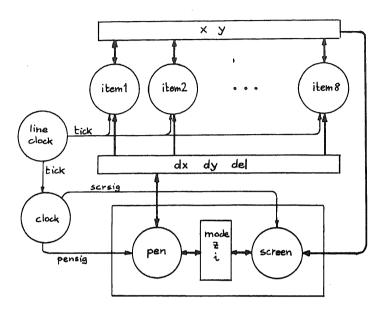

Our objective is to design a system which represents two data streams. Stream 1 originates at the keyboard and flows to the typewriter printer. Stream 2 leads from the card reader to the line printer. Both streams are sequences of characters (ASCII code), and all four devices are to be buffered. The streams are to flow independently; hence, the system consists of two entirely independent, uncoupled parts. Each part is represented by a system consisting of three processes and has the structure shown in Fig.1.

Fig.1, Data flow and system structure

The buffers (and their associated variables) constitute the interfaces between the processes. Hence, it is appropriate to postulate two interface modules. The buffers and the routines depositing and fetching data in and from the buffers are the natural components of each interface module which provides mutual exclusion of interacting processes. Since each buffer is associated with a unique device, and therefore also with a device driver process, the interface module is declared as a device module (whose servicing priority is defined by the PDP-11 hardware). According to the rules of Modula, a process is

declared entirely within the interface module, if it is a driver process.

Normal buffer interface module:

```

interface module M;

var buffer: T;

procedure deposit( ); ... (*used by producer process*)

procedure fetch( ); ... (*used by consumer process*)

end M

```

Buffer interface module, if the consumer process is a driver process:

```

device module M [priority];

orocedure deposit( ); ... (*used by the producer*)

process consumer;

begin initialise;

loop fetch;

initiate consumer device; doio

end

end consumer

end M

```

Buffer interface module, if the producer is a driver process:

```

device module M [priority];

procedure fetch( ); ... (*used by consumer*)

process producer;

begin initialise;

loop initiate producer device;

doio; deposit

end

end producer

end M

```

#### 2.1. The keyboard to typewriter stream.

This example shows the simplest possible case. Its simplicity is threefold:

- 1. Both devices use the same encoding of information (ASCII).

- 2. Both devices operate on the basis of single character  $\mbox{ trans-}$  mission.

- 3. The devices require no status interrogation.

The main process is chosen to be as simple as possible. Its sole obligation is to transfer individual characters from the input buffer to the output buffer. The only additional duty is to recognise carriage return control characters (cr), and to generate an additional line feed character (lf) following each cr.

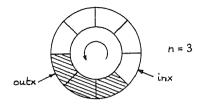

Each of the two interface modules contains a data buffer; these buffers are used as cyclic buffers. With each buffer are associated a variable n indicating the number of currently filled buffer elements, and two indices (inx and outx) designating the locations of the next characters to be fetched

and deposited (see Fig.2). Also associated are two signals. The signal "nonempty" is sent each time a character is put into the buffer and implies the condition  $n>\emptyset$ , and "nonfull" is sent each time a character is taken from the buffer and implies n< N, where N is the buffer's size.

Fig. 2, Cyclic buffer with 8 slots

The typewriter stream part is represented by the two device modules "keyboard" and "typewriter", each containing a buffer and a device driver, and of the main process "stream 1".

Each of the two buffers is accessed by a producer and a consumer process: n denotes the number of characters in the buffer.

Producer: logo produce a character;

if n = N then wait(nonfull) end;

deposit the character in buffer;

inc(n); send(nonempty)

end

Consumer:  $loop if n = \emptyset then wait(nonempty) end;$

fetch next character from buffer;

dec(n); send(nonfull);

consume the character

end

The last three lines of the Producer and the first three of the Consumer are formulated as parts of a device interface module to ascertain mutual exclusion.

The important property of this solution is that no reference to machine and device dependent facilities is made outside the device modules, and that even within these modules the programs are straight-forward, referring to hardware defined facilities only in a few instances.

These are:

- 1. the device  $\underline{S}$ tatus registers KBS and TWS,

- 2. the device Buffer registers KBB and TWB,

- 3. the device interrupt addresses 60B and 64B,

- 4. the interrupt priority 4.

Bit 6 in each status register is the interrupt enable bit. The statement xxS[6] := true (preceding "doio") enables, the statement xxS[6] := false (following "doio") disables interrupts.

Of course, in realistic applications the drivers are very short programs compared to the remainder of the system. Here the

opposite is true, because the most trivial case of a main process was chosen in order to be able to concentrate on demonstrating Modula's capability to express driver processes and device operations in a readable, "high-level" programming style (see program at the end of this chapter).

# 2.2. The card reader to line printer stream

The mechanism for the transmission of data from a card reader to a line printer is more complicated, although based on the same principle of buffering for each device. There exist four reasons for complications:

- 1. The line printer uses the 7-bit ASCII encoding of characters, whereas the card reader delivers a different encoding. We shall let the drivers accept and deliver data encoded as dictated by their devices, and let the main process perform the task of translation (see procedure convert).

- 2. The card reader, once activated, reads a full card, i.e. a portion of 80 characters. Hence, the buffer space reservation scheme must be somewhat different from the one used above.

- 3. If data transfer rates are high, it is inappropriate to exchange synchronization signals after each character transmission. Data are "blocked" and signals are sent only after transfer of each block. We demonstrate this solution in the case of the line printer, where each line is taken as a block.

- 4. The card reader status must be interrogated before and after reading each card. If it is in the "not ready" state, interrogation must be repeated periodically, because the card reader does not send a signal when returning to the ready state.

We notice that all four complications are not just due to the programmer's like for sophistication, but are caused by the inherent characteristics of the various devices and data carriers. We first describe the modifications to the input buffer scheme.

The circumstance that input data are delivered in portions of 80 characters requires that before starting the card reader, space for at least 80 characters must be free in the buffer. This entire portion must be reserved to the reader process during the time of reading the card. At the same time, the remainder of the filled buffer should be accessible to the consumer. Hence, a single variable n to indicate the number of filled elements does not suffice, since the number of empty portions is not necessarily N-n, when N is the total buffer size. In place of a single counter n, two variables nf and ne are introduced to denote the numbers of filled and empty slots respectively. The invariant

holds at all times, where m1 and m2 are the portion sizes claimed by producer and consumer respectively. (Actually m1  $\pm$  81, since each card end is represented by a marker). In order to reduce the number of signalling operations, the "sleeping barber" scheme is used [2]. It is sketched by the following program excerpt:

Producer: loop dec(ne,m1); if ne < 0 then wait(nonfull) end: deposit portion with size m1; inc(nf,m1); if nf  $\geq$  0 then send(nonempty)end

end

Consumer: loop dec(nf,m2); if nf <  $\emptyset$  then wait(nonempty) end; fetch portion with size m2; inc(ne,m2); if ne  $\ge \emptyset$  then send(nonfull) end end

In the card reader driver the statement CRS :=  $[\emptyset,6]$  sets the interrupt enable bit and at the same time initiates the reader motion. A completion interrupt is sent after receiving each column in CRB. This is represented by the statement doio in the usual way. It is followed by a test of bits 14 and 15, the former indicating that the end of the card is reached and a next card is in the hopper, the latter indicating that an "abnormal" condition exists, such as an empty hopper. Before starting a card motion, status bits 8 and 9 are tested. If bit 8 is set, the reader is not ready. It becomes ready when the operator pushes the RESET button. This action, however, does not send an interrupt signal to the computer. Hence, the status has to be polled repeatedly. Such a polling process is easily expressed by a statement of the form

# while test fails do wait(s) end

if one can assume the availability of a signal s that is sent periodically at certain time intervals.

Such periodic signals are customarily produced by so-called clocks, i.e. devices that interrupt the processor at given intervals, usually that given by the line frequency. (50 or 60 cycles/sec). In the present program, the "clock" appears as a device like other peripherals. However, it does not have to be triggered into producing the next pulse; instead, the driver process merely needs to wait for the next pulse to occur. This waiting is expressed by the statement "doio" (which in this case is obviously a misnomer). As a consequence, the process merely consists of the statement

## loop doio; send(tick) end

We are now tempted to substitute the clock signal (which is appropriately called "tick") for the signal s. However, this would violate the (peculiar) implementation restriction of Modula which specifies that no signal sent by a device process may be received by a device process. The difficulty is resolved by inserting yet another process — which is not a device process — between the sender and the receiver. This process is called

"clock". The clock driver process is enclosed in a device module (called "timing"), from which only the signal "tick" is exported. Note that Modula specifies that no process may execute a send operation upon an exported signal; hence, the device process is the only process that can send the tick signal.

The line printer buffering scheme is similar to that of the card reader in so far as signals are exchanged after receiving portions of data instead of after each character. In contrast to the card reader, however, the portions do not have a fixed size. We take the line as the natural choice of a portion, i.e. each end of a line, represented by a line-feed control character, causes a signal to be sent to the driver. Line printers usually have their own "hardware" buffer, in which characters are accumulated, until a line-feed character is received, whereupon the actual printing occurs. This explains the property that individual characters are accepted verv auickly. instantaneously, because they are only stashed away in the internal buffer. As a consequence, it is unwise to wait for an interrupt from the printer in this case. Instead, the status register LPS is tested immediately after putting a character into the buffer register LPB. If Bit 7 is not set, printing takes place, and we may as well wait for the completion signal (interrupt) by executing "doio". (Note that printing is not caused exclusively by line-feed, but also as soon as the line buffer is filled. Therefore the test for the necessity of waiting must not depend on the value of the character output).

We presume, however, that the sender knows whether a special line-feed is sent (a line is closed) or an ordinary character is to be printed. The action of terminating a line is therefore expressed by an explicit procedure "weol" (write end of line), that is used to send a signal to the driver. The variable of does not count the number of single characters in the buffer "buf", but instead counts the number of lines.

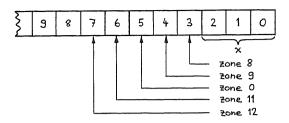

The main process "stream 2" merely receives characters from the card reader and transmits them to the line printer. Its function is to convert the character encodings. The line printer requires ASCII code, whereas the card reader delivers integers. Their binary representation is obtained in the way shown in Fig. 3 from the card hole combinations (this mapping is a hardware facility); the value x represents the position of a single punch in zones 1 to 7.

Fig.3, Card punch encoding

A special end-of-file card is recognised as one which has a 7-8-9 hole combination in column 1. It is translated into an integer value -1, and in turn to a form-feed character which causes a page eject on the line printer.

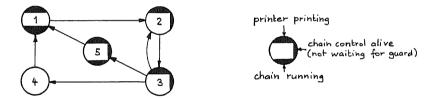

In order to show the convenience of the process and signal facilities, we shall introduce yet another complication that demonstrates a frequently occurring situation and originates from a very practical problem. We assume that the printer is a chain printer, and that the chain drive can be started and stopped under program control. We pose the condition that the chain motor is to be stopped, if no printing is requested for a period longer than a certain time period t. This is desirable to save the printer from undue wear. Naturally, the chain has to be restarted as soon as information has to be printed. As the starting of the chain is subject to a certain delay during which the printer is inoperable, the idle period t has to be chosen carefully. About 10 sec have proved to be a sensible value.

"frequently occurring situation" referred to above is the condition in which a "process" is waiting for any one of several events. In our case it is the printer process having encountered an empty buffer, which is waiting for either new information to enter the buffer in order to be printed, or for the printer chain to be stopped after the time interval t has elapsed. This problem is solved in the following way: A new process is introduced with the purpose to control the printer chain movement. It is therefore called "chaincontrol", and consists of a simple loop containing two statements. The first of them, "testchain", contains a wait statement, which "puts this process to sleep" while the printer is active. As soon as the printer driver recognises an empty buffer, it signals chaincontrol to become active. A delay counter "del" initialised which determines the number of times chaincontrol executes its loop "testchain; wait(tick)". The second statement is merely a delay (20 msec) and demonstrates another use of the clock signal. If, during one of the executions of "testchain", it is discovered that the printer has resumed operation by finding of  $\geq \emptyset$ , chaincontrol is immediately "put to sleep" again. If, on the other hand, the printer had remained inactive during the specified number of tests, an appropriate control character is output, causing the chain to stop, whereafter chaincontrol, having performed its task, waits for the next time

the printer needs to be guarded. The system consisting of the processes "chaincontrol" and printer driver assumes the following possible states:

| _ |   | driver         | chaincontrol | nf | del | chain   |

|---|---|----------------|--------------|----|-----|---------|

|   | 1 | active         | wait(guard)  | ≥Ø |     | running |

|   | 2 | wait(nonempty) | active       | <Ø | >Ø  | running |

|   | 3 | wait(nonempty) | wait(tick)   | <Ø | > Ø | running |

|   | 4 | wait(nonempty) | wait(guard)  | <Ø | = Ø | stopped |

|   | 5 | active         | active       | ≥Ø | •   | running |

Transition 1-2 is caused by the driver sending the signal "guard", transitions 2-3 and 3-2 are implied by the execution of the control process, the latter by receiving the signal "tick". 3-4 occurs through the signal tick, and the control process issuing a dc4 character after decrementing del to  $\emptyset$ . Transition 4-1 occurs if new information enters the buffer, whereas 3-5 occurs for the same reason, but while the chain had not been stopped yet.

Fig.4, State transitions of printer system

Note that the procedure "testchain" is an interface procedure. Therefore it is guaranteed that during its execution the driver either waits (nf  $< \emptyset$ ) or performs output operations (nf  $\ge \emptyset$ ).

We conclude the presentation of this program by a diagram showing its various processes and their interfaces represented by buffers and signals.

Fig.5, Interactions of processes via buffers and signals

```

module datastreams:

const lf = 12C; ff = 14C; cr = 15C;

var crsig: signal;

device module timing [6];

define tick:

var tick: signal;

lcs [177546B]: bits; (*clock status*)

process driver [1008];

begin lcs[6] := true;

loop doio; send(tick)

end

end driver :

begin driver

end timing ;

device module keyboard [4];

define get;

const n = 16; esc = 33C;

var inx, outx, nf: integer;

nonfull, nonempty: signal;

buf: array 1:n of char;

procedure get(var ch: char);

```

```

begin

if nf = \emptyset then wait(nonempty) end :

ch := buf[outx]; outx := (outx mod n) + 1;

dec(nf); send(nonfull)

end get :

process driver [60B]:

kbs [17756ØB]: bits; (*status*)

kbb [177562B]: integer; (*buffer*)

var kbs [177560B]: bits:

ch: char:

begin

1000

if nf = n then wait(nonfull) end :

kbs[6] := true; doio; kbs[6] := false;

ch := char(kbb mod 200B):

if ch = esc then halt(\emptyset) end :

buf[inx] := ch; inx := (inx mod n) + 1;

inc(nf): send(nonemoty)

end

end driver :

begin inx := 1: outx := 1: nf := 0: driver

end keyboard :

device module typewriter [4]:

define but:

const n = 64;

(*buffer size*)

var inx, outx, nf: integer:

nonfull, nonempty: signal;

buf: array 1:n of char:

procedure put(ch: char);

begin

if nf = n then wait(nonfull) end :

buf[inx] := ch; inx := (inx mod n) +1;

inc(nf); send(nonempty)

end put :

process driver [64B]:

var tws [177564B]: bits:

(*status*)

twb [177566B]: char:

(*buffer*)

beain

1000

if nf = 0 then wait(nonempty) end :

twb := buf[outx]; outx := (outx mod n) + 1;

tws[6] := true; doio; tws[6] := false;

dec(nf); send(nonfull)

end

end driver :

begin inx := 1; outx := 1; nf := 0; driver

end typewriter:

device module cardreader [6];

define read;

use crsig;

const n = 256: (*buffer size*)

```

```

var inx, outx, ne, nf: integer;

nonfull, nonempty: signal:

buf: array 1:n of integer:

procedure read(var x: integer);

begin dec(nf);

if nf < Ø then wait(nonempty) end :

x := buf[outx]: outx := (outx mod n) + 1;

inc(ne): if ne >= 0 then send(nonfull) end :

end read ;

process driver [2308];

const m = 81: (*block size*)

var crs [1771608]: bits; (*status*)

crb [177164B]: integer:

(*buffer*)

procedure put(x: integer):

begin buf[inx] := x: inx := (inx mod n) + 1;

inc(nf)

end put :

begin

loop dec(ne,m):

if ne < Ø then wait(nonfull) end :

while not off(crs, [8,9]) do wait(crsig) end ;

crs := [\emptyset, 6]; (*start card motion*)

loop doio:

when not off(crs, [14,15]) exit

put(crb)

end:

put(-1): crs[6] := false: (*end of line mark*)

if nf >= 0 then send(nonempty) end

end driver :

begin inx := 1; outx := 1; nf := 0; ne := n; driver

end cardreader :

device module lineprinter [4]:

define write, weol, testchain;

use lf;

const n = 512;

(*buffer size*)

dc3 = 23C; dc4 = 24C;

chaindelay = 250:

(* 10 sec *)

var inx, outx, ne, nf, del: integer;

nonfull, nonempty, guard: signal:

buf: array 1:n of char;

lps [177514B]: bits:

(*status*)

lpb [177516B]: char:

(*buffer*)

procedure write(ch: char):

begin dec(ne):

if ne < 0 then wait(nonfull) end :

buf[inx] := ch; inx := (inx mod n) + 1;

end write :

procedure weal; (*write end of line*)

```

```

begin inc(nf); send(nonempty)

end weol :

procedure testchain:

begin

if nf >= 0 then wait(guard)

else dec(del):

if del = 0 then

lob := dc4: wait(guard)

end

end

end testchain:

process driver [2008]:

var ch: char:

begin lpb := dc3:

loop dec(nf):

if nf < Ø then

send(guard); wait(nonempty);

lpb := dc3; del := chaindelay

end:

repeat ch := buf[outx]; outx := (outx mod n) + 1;

inc(ne); lpb := ch;

if not lps[7] then

lps[6] := true; doio; lps[6] := false

end

until ch = lf;

if ne >= 0 then send(nonfull) end

end

end driver :

begin inx := 1; outx := 1; ne := n; nf := 0; driver

end lineprinter :

process stream1; (*keyboard to typewriter*)

use get, put;

var ch: char;

begin

loon get(ch);

if ch = cr then put(cr); put(cr); put(lf)

else put(ch)

end

end

end stream1 :

process stream2; (*cardreader to lineprinter*)

use read, write, weol;

const eoi = 37B; badchar = '?':

var x: integer; ch: char;

t: array 0:63 of char; (*translation table*)

z: array Ø: 7 of integer:

procedure convert:

(*x to ch*)

var zone, digits: integer;

begin zone := x div 32; digits := x mod 32;

zone := z[zone];

if zone < 0 then ch := badchar else

```

```

if digits >= 16 then digits := 9 end:

ch := t[16*zone+digits]

end

end convert :

begin

z[\emptyset] := \emptyset ; z[1] := 3 ; z[2] := 2 ; z[3] := -1 ;

z[4] := 1 ; z[5] := -1 ; z[6] := -1 ; z[7] := -1 ; t[0] := ' : t[1] := '1' : t[2] := '2' : t[3] := '3' :

t[4]:='4'; t[5]:='5'; t[6]:='6'; t[7]:=

::: t[11] := :t[15] :=

t[8]:= '8'; t[9]:= '9'; t[10]:=

t[12]:= '#'; t[13]:= '@'; t[14]:=

t[16] := '+'; t[17] := 'A'; t[18] := 'B'; t[19] :=

'F': t[23] :=

t[20] := 'D'; t[21] := 'E'; t[22] :=

'<': t[27] :=</pre>

t[24] := 'H'; t[25] := 'I'; t[26] :=

t[28] := ')'; t[29] := '\'; t[30] :=

...

; t[31] :=

t[32] := '-'; t[33] := 'J'; t[34] :=

'K'; t[35] :=

t[36] := 'M': t[37] := 'N': t[38] :=

'0': t[39] :=

t[4\emptyset] := 'Q'; t[41] := 'B'; t[42] := t[44] := '*'; t[45] := [1'; t[46] := '*']

; t[43] :=

. ? .

'; t[47] :=

t[48] := '\emptyset'; t[49] := '/'; t[50] := 'S'; t[51] :=

t[52] := 'U'; t[53] := 'V'; t[54] := 'W'; t[55] :=

t[56] := 'Y'; t[57] := 'Z'; t[58] := ']'; t[59] := ',

t[60] := '('; t[61] := '_'; t[62] := '"'; t[63] := 'G

loop read(x);

if \times = eoi then

repeat read(x) until x < \emptyset;

write(ff): (*form feed*)

else

while \times >= \emptyset do

convert; write(ch); read(x)

write(lf); weol (*line feed*)

end:

end

end stream2:

process clock;

use tick, crsig;

begin

loop wait(tick): send(crsig)

end

end clock ;

process chaincontrol;

loop testchain: wait(tick)

end

end chaincontrol;

begin (*datastreams*)

stream1; stream2; clock; chaincontrol

end datastreams .

```

# 3. THE PROGRAM "DISKTAPE"

With the second program we continue and elaborate on the subject of device handling and sequential data transfer. The devices under consideration are a disk unit and a terminal containing two tape cassette drives. These devices are in several respects more complicated than those discussed in the preceding section, and therefore require also some more sophistication in the design of their operators. The equipment used in this particular experiment consists of a DEC RK-11 disk cartridge unit and an HP2644A terminal [3]. This terminal contains a microprocessor that is used to send and receive instructions to operate the two tape cassettes.

Let us first list the specifications of the program to be designed.

- 1. Let the disk store consist of 8 files with a fixed maximum length.

- Commands are to be given from the terminal keyboard. There shall be commands for copying a file from tape to disk, and vice-versa, for rewinding, selecting, and marking tapes, and for skipping files on a tape.

- 3. Specifically, the commands are Rn: read tape onto disk file n (1  $\leq$  n  $\leq$  8). Wn: write disk file n onto tape.

- Cs: control operation; the character string s is determined by the specifications of the HP terminal.

- 4. Every command is to be terminated by a period. The system obeys the commands as soon as the "command line" is terminated (line-feed character). A line may contain several commands.

- When typing a command, the entire command line can be cancelled by typing a backspace character.

The task thus defined appears as more difficult than the preceding problem for several reasons.

- Instead of a number of continuous data streams, there is essentially one channel on which data are transferred according to input commands that must be interpreted.

- The disk is a device which requires an address of the location where the data are stored.

- 3. The disk is a device that can read and write data.

- 4. The disk transfer rate is so high that we must avoid entering a device module for each character to be transferred.

- 5. The terminal is a device that requires a certain prescribed "protocol" to transfer data to and from the tapes. It also requires initiation and acknowledgement messages (also called "handshaking" procedures).

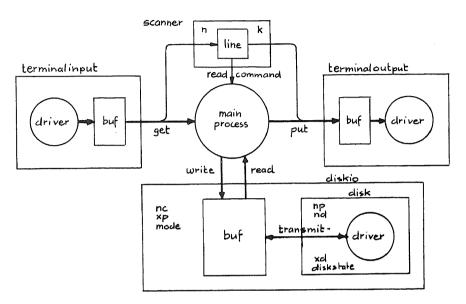

The overall structure of this system is therefore given by the devices involved. There are four processes: a terminal input, an output, a disk driver, and a main process controlling the transfers. The structure is shown in Fig.6, and the main process indefinitely repeats the following three statements:

terminal input process put put terminal output module.

read write

disk

module.

Fig.6. System structure with 3 device modules.

### 3.1. Module structure and interfaces

We start out by defining the interfaces between the modules, i.e. the procedures by which communication takes place. The terminal input module defines a procedure called <a href="mailto:oet">oet</a>. It "gets" a character from the terminal. Similarly the output module defines a procedure <a href="mailto:output">out</a>. The disk module, allowing transfers in both directions, defines procedures <a href="mailto:read">read</a> and <a href="write">write</a>. Naturally, these operations cannot be performed at the same time. The disk either reads or writes: its state is characterised by a mode variable. The disk module therefore defines another procedure, called <a href="mailto:open">open</a>, to set this mode. Accordingly, a procedure <a href="mailto:close">close</a> is defined to indicate termination of a file transfer, and to make the disk available for further operations.

The two modules which buffer the HP 2644A terminal are exactly like the ones used in the program of chapter 2. They implement a simple, cyclic buffer. Both buffers must be capable of holding at least one line of text (which is the unit of data transferred to and from tape at 2400 baud).

Before embarking on the explanation of the disk module, explain the details of the main process. Because interpretation of a command shall begin only after the reading of an entire line, and because commands arrive from the same source as the data to be transferred, a further buffering of commands evidently necessary. This calls for another module, which we shall call <u>scanner</u>. It contains a buffer called <u>line</u>, and acts not unlike the scanner of a compiler, reading lines of text and delivering a command each time called upon. This command is a character sequence stored in the variable com. Note that the scanner also takes care of system specification 5 which demands that an input line can be cancelled by typing a backspace character. The variable n, appropriately hidden inside the scanner, counts the number of commands in the line. k is the index of the last character read from the command line. (See

program at the end of this chapter.)

#### 3.2. Interpretation of commands

We can now proceed to an explanation of the detailed operations performed when interpreting a command. The first character (R,W,or C) identifies the command. In the cases of the R and W commands, the second character denotes the disk file to be written or read. In order to understand the data transfer mechanism, we must know the representation of text as received from and as required by the terminal. The essentials are as follows:

Data are read from and written onto tape by sending a "command" to the terminal. It consists of a sequence of characters starting with an escape character. The sequence is therefore called an <u>escape</u> sequence. The sequence

esc & p Ø R dc1

causes the terminal to read a line of text from the designated tape and to send it to the computer. The line is terminated by a  $\underline{cr}$  and an  $\underline{lf}$  character. (We assume that the HP 2644A terminal is strapped for line block transfer with straps D, G in, E, H out [4]). If the end of the file has been reached, a tape mark is encountered, which results in the transmission of a "line" consisting of the single control character  $\underline{rs}$  (record separator), followed by  $\underline{cr}$ ,  $\underline{lf}$ . Hence, it is always necessary to check the first character of each line received in order to detect the end of the file.

When writing on a tape, the escape sequence esc & p W

is used. It causes the terminal to accept a sequence of data characters terminated by cr, lf, dc1. Since we shall store the data on disk in exactly the form as received from the terminal, we must again test the first character in each line. If it is rs, then a file mark has to be written instead of transmitting the "line". This is done by sending the escape sequence

esc & p 5 C dc1

After sending each line, an acknowledgement is requested from the terminal by sending a dc1 character. This acknowledgment consists of a letter S (success) or F (failure), followed by cr,lf. In our program, the acknowledgement is not interpreted; but it should obviously be done in a system acceptable for practical purposes.

The third command (C) is introduced merely to make available in a primitive manner the entire set of possibilities to control the terminal from the computer. The command  $C_{\underline{\mathbf{s}}}$ , where  $\underline{\mathbf{s}}$  stands for any character sequence, is returned to the terminal as an escape sequence

esc & p s dc1

which may serve to designate source and destination tapes, to rewind tapes, to mark them, or for many other operations [4].

#### 3.3. The disk module

Communication with the disk brings up two problems that have not been encountered when dealing with strictly sequential, unidirectional devices.

- After transferring a file, the disk must be "released" in order to become available for the execution of another file transfer, whose direction may differ from the preceding one.

- 2. The high transfer rate of a disk requires that its interrupts be serviced with a high processor priority. It is desirable that the processor enters that priority level as rarely as possible. Communication with the device process must take place at that level, and should therefore be necessary only after transfer of relatively large blocks of data, and certainly not for each character.

The frequently adopted solution to problem 1 is that instructions (requests) for disk operations are queued in a buffer along with their parameter (disk address, buffer address, mode of transfer, etc.). We will refrain from request buffering, and show a solution that requires a much stricter synchronization of the two participating processes.

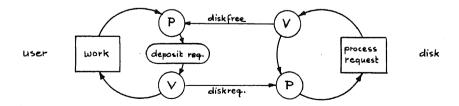

Assume that there are variables to hold the instruction parameters listed above. During an entire disk operation (file transfer) they belong exclusively to the disk driver process. Only after its termination and until the initiation of the next operation do they belong to the requestor (subsequently called "user"), which at this time may assign the parameters of the next request to them. This is an obvious situation where semaphores [2] are used to delay a process before passing a certain point, as is shown in Fig.7. We call the semaphore that delays the program before transmitting its next request "diskfree" (because the semaphore "opens" when the disk process is free to accept the next request), and we call the semaphore that delays the disk driver until the next request is deposited "userfree", because it opens when the user is free to work after having deposited the request.

Fig.7. Requestor / acceptor synchronization with two semaphores.

According to Hoare [5], we express a (binary) semaphore by a pair consisting of a signal and a Boolean variable which

remembers whether a signal had been sent. The semaphore "diskfree" is represented by the signal of the same name and the Boolean variable "diskbusy" and the operations P and V become

P: <u>if</u> diskbusy <u>then</u> wait(diskfree) <u>end</u>; diskbusy := true

V: diskbusy := false; send(diskfree)

Similarly, the semaphore "userfree" is represented by the signal of the same name and the Boolean variable "userbusy". The two processes in Fig.7. are then expressed as follows:

user: loop if diskbusy then wait(diskfree) end: diskbusy := true: deposit disk request; userbusy := false: send(userfree): reneat produce/fetch data: deposit/consume data until end of file

end

disk: loop diskbusy := false; send(diskfree); (\*now disk request parameters are loaded by "user"\*) if userbusy then wait(userfree) end: userbusy := true: reneat fetch/read data: write/deposit data until end of file end

We notice a strong symmetry between the two processes, although in their roles they are dissimilar: the disk process is the slave of the user. In Modula, the disk process is formulated as a device process. The fact that device processes are served with a higher priority has in this case a notable consequence [7]: The send operation does not "release" the processor. Hence, no action can possibly intervene before the succeeding statement wait(userfree). We know that userbusy has the value true, because the only way it can obtain the value false is through the user process having received the signal diskfree. The consequence is that the variable userbusy can be deleted entirely, and the semaphore reduces to a signal, (which we rename "diskrequest").

Programming experience has shown that the mistake to use a simple signal where actually a semaphore would be needed, is one of the most frequent sources of system deadlocks. The reason is that a signal is only effective at the time it is sent; if no process is waiting for it, the signal is forgotten. The Boolean variable in the semaphore serves to remember that a signal was emitted (the general semaphore even counts them). The deadlock then arises when a process decides to wait for a signal that incidentally - had been sent already when there was no one to receive it.

We now turn our attention to the second problem: avoiding to enter the driver module for fetching or depositing each single character. We note that the disk reads and writes blocks of characters, so-called <u>sectors</u> with a fixed size of 512 characters (256 words). Hence, the solution lies in nesting the device module inside an interface module. The latter is entered for each character transmitted, the former for each sector.

We first consider the device module called <u>disk</u>. It contains, apart from the driver process, the three procedures opendisk, transmitsector, and closedisk, and the variables np, nd, disk-state, and the disk registers. The disk address register and the diskstate are initialised by the procedure opendisk. np and nd replace the usual counters nf and ne, and denote the numbers of sectors available to the programm (user) and the disk respectively. This change in nomenclature is essential, because the disk sometimes assumes the role of the producer, sometimes of the consumer. Now each of the two partners operates in a fixed way on its own counter, independently of the direction of data transfer. This is epitomized by the single procedure "transmitsector" replacing a readsector /writesector pair. (Note that np and nd do not include the sectors upon which the program or the disk are currently operating.)

Whereas the disk module views the buffer as a collection of sectors, the outer module, called <u>diskin</u>, views it as a buffer of single characters. In particular, it contains a counter variable no counting the <u>number</u> of <u>characters</u> available for reading, or of empty slots available for writing in the sector currently belonging to the program. Once this count reaches zero, a new sector is transmitted (changes ownership). But only in this instance is the device module entered.

A few details may help the reader to comprehend the disk modules: A variable "mode" denotes the current state of the disk module (idle, reading, writing). It is used to set the value of the device module's analogous variable "diskstate", and to determine the actions needed upon closing a file. Moreover it could serve for checking the legality of calls of the read and write procedures.

The disk is initialised by setting the disk address register, the buffer address register, a word counter, and the control and command register. The latter requires setting of the following bits: 6 for interrupt enable, 2 for reading, 1 for writing, and Ø for starting the operation.

The disk driver needs to be able to recognise the last sector of a file to be read or written. A simple solution lies in embedding this information in the last sector itself. This is done in our example by giving the last character of the last sector the value <u>fs</u> (file separator), assuming that this character does not otherwise occur. In writing a file, this character is inserted by the procedure "close". It is recognised by the disk driver upon reading <u>and</u> writing. Note that the variable "diskstate" combines the functions of the Boolean "diskbusy" and of the driver's mode of operation.

The file system presented here is primitive with respect to disk

store allocation. It assumes a fixed allotment of 48 sectors (= 24575 characters) per file, because it was not the purpose of this exercise to develop a flexible storage allocator. The entire program is listed subsequently and is to be consulted for further details; the overall process— and module structure is shown in Fig.8.

Fig.8. Module and process interconnections

```

module disktape;

const 1f = 12C; cr = 15C; rs = 36C; dc1 = 21C:

esc = 33C; bs = 10C; bel = 7C; fs = 34C;

var ch, fch: char;

i: integer:

com: array 1:80 of char;

(*current command*)

device module terminalinput [4]:

define get;

use ch;

const del = 177C; bufsize = 256;

var n, in, out: integer;

nonempty, nonfull: signal;

buf: array 1:bufsize of char;

orocedure get:

begin if n = \emptyset then wait(nonempty) end :

ch := buf[out]; out := (out mod bufsize) + 1;

dec(n); send(nonfull)

end get :

orocess driver [300B]:

var ts [ 17561ØB]: bits;

```

```

tb [175612B]: integer;

ch: char;

begin

loop if n = bufsize then wait(nonfull) end ;

ts[6] := true; doio; ts[6] := false;

ch := char(tb mod 200B);

<u>if</u> ch = del \underline{then} halt(\emptyset) \underline{end};

buf[in] := ch; in := (in mod bufsize) + 1;

inc(n); send(nonempty)

end

end driver :

begin n := \emptyset; in := 1; out := 1; driver

end terminalinput :

device module terminaloutout [4]:

define put;

const bufsize = 256:

var n, in, out: integer:

nonempty, nonfull: signal:

buf: array 1:bufsize of char:

procedure put(x:char);

begin if n = bufsize then wait(nonfull) end ;

buf[in] := x; in := (in mod bufsize) + 1;

inc(n); send(nonempty)

end put ;

process driver [3048]:

var ts [1756148]: bits;

tb [175616B]: char:

begin

loop if n = \emptyset then wait(nonempty) end :

tb := buf[out]; out := (out mod bufsize) + 1;

ts[6] := true; doio; ts[6] := false;

dec(n); send(nonfull)

end

end driver :

begin n := 0; in := 1; out := 1; driver

end terminaloutout:

interface module diskio;

define open, read, write, close:

use ch,fs:

const nsec = 4:

(*no. of sectors*)

sectorsize = 512:

bufsize = 2048:

(*bufsize = nsec*sectorsinze*)

maxsectors = 48:

(*max no. of sectors per file*)

nfl = 8:

(*no. of files*)

var mode: integer;

(*Ø=free, 1=read, 2=write*)

nc: integer:

(*no. of chars in current sector*)

ns: integer:

(*no. of sectors written*)

xp: integer:

(*buffer index of program*)

current: integer:

(*index of current file*)

file: array 1:nfl of

record adr, size: integer

```

```

end :

buf: array 1:bufsize of char:

device module disk [5]:

define opendisk, transmitsector, closedisk;

use buf, bufsize, sectorsize, nsec, fs:

var np, nd: integer: (*no. of sectors available*)

sp, sd: signal:

diskstate: bits:

diskreq, diskfree: signal:

rkds [177400B]: bits:

(*drive status*)

rker [1774028]: bits;

(*error status*)

rkcs [1774Ø4B]: bits:

(*control status*)

rkwc [1774Ø6B]: integer:

(*word count*)

rkba [177410B]: integer;

(*buffer address*)

rkda [177412E]: integer: (*disk address*)

procedure opendisk(m.a: integer):

(*initialise disk in mode m at address a*)

begin if diskstate[6] then wait(diskfree) end :

if m = 1 then

diskstate := [\emptyset,2,6]: nd := nsec: np := \emptyset

diskstate := [0,1,6]: nd := 0: np := nsec

rkda := a + 20000B: send(diskrea):

dec(np); if np < 0 then wait(sp) end

end opendisk :

procedure transmitsector:

begin inc(nd); if nd >=0 then send(sd) end ;

dec(np): if np < \emptyset then wait(sp) and

end transmitsector:

procedure closedisk:

begin inc(nd); if nd >=0 then send(sd) end

end closedisk:

process driver [2208];

const wps = 256;

(*wps = bufsize/2*)

var endchar: char:

(*buffer index*)

xd: integer:

loop wait(diskreq): xd := 1;

repeat dec(nd):

if nd < Ø then wait(sd) end :

rkwc := -wps: rkba := adr(buf[xd]);

rkcs := diskstate; doio; rkcs[6] := false;

if rkcs[15] = 1 then halt(15) end;

inc(xd,sectorsize); endchar := buf[xd-1];

if xd > bufsize then xd := 1 end :

inc(np); if np >= \emptyset then send(sp) end

until endchar = fs:

diskstate := []; send(diskfree)

end driver :

```

```

begin diskstate := []; driver

end disk :

procedure open(m: integer; k: char);

(*open file k in mode m*)

begin mode := m; nc := sectorsize; ns := 0; xp := 1;

current := integer(k) - integer('0');

if (m = 1) and (file[current].size = 0) then halt(3) end :

opendisk(m, file[current].adr)

end open :

procedure write:

begin (*assume mode = 2, nc < sectorsize, ch <> fs*)

buf[xp] := ch: inc(xp); dec(nc);

if nc = \emptyset then

if xp > bufsize then xp := 1 end ;

transmitsector; nc := sectorsize;

inc(ns): if ns = maxsectors then halt(1) end

end

end write :

procedure read:

begin (*assume mode = 1*)

if nc = 0 then

if xp > bufsize then xp := 1 end ;

transmitsector: nc := sectorsize

ch := buf[xp]; inc(xp); dec(nc)

end read ;

procedure close:

begin (*assume mode = 1 or 2*)

if mode = 2 then

buf[xp+nc-1] := fs:

inc(ns): file[current].size := ns

end:

closedisk: mode := Ø

end close :

begin (*interface module diskio*)

mode := Ø; current := nfl;

repeat file[current].adr := current * 64;

file[current].size := 0: dec(current)

until current = 0

end diskio:

module scanner:

define readcommand:

use ch, com, lf, bs, get, put;

var k,n: integer:

line: array 1:80 of char;

procedure readline:

var i: integer;

(*assume linelength <= 80*)

```

```

<u>begin</u> put('*'); i := 0; k := 0;

repeat get:

if ch = bs then (*cancel*)

put(' \setminus '): i := \emptyset: n := \emptyset:

inc(i); line[i] := ch; put(ch);

if ch = '.' then inc(n) end

end

until ch = lf

end readline :

procedure readcommand:

var j: integer:

begin

while n = \emptyset do readline end :

dec(n); j := \emptyset;

reneat inc(j); inc(k): com[j] := line[k]

until line[k] = '.

end readcommand:

begin n := Ø

end scanner :

procedure escseq;

begin put(esc); put('G'); put('p')

end escseo :

procedure acknowledge:

begin put(dc1); get;

if ch <> 'S' then put(ch): put(bel) end;

repeat get until ch = lf

end acknowledge:

begin (*main*)

loop readcommand:

<u>if</u> com[1] = 'C' <u>then</u>

(*control*)

escseq; i := 2;

while com[i] <> '. do

put(com[i]); inc(i)

end:

acknowledge

elsif com[1] = 'R' then

(*read tape*)

open(2,com[2]):

reneat (*read a line*)

escseq; put('Ø'); put('R'); put(dc1);

get: fch := ch; write;

reneat get; write

until ch = lf

until fch = rs:

close

elsif com[1] = 'W' then

(*write tape*)

open(1,com[2]); read;

while ch <> rs do

escseq; put('W'); put(ch);

repeat read; put(ch)

until ch = lf;

acknowledge; read

```

```

end :

escseq; put('5'); put('C'); (*mark tape*)

acknowledge; close

end ;

put(bel)

end

end disktape .

```

### 4. THE PROGRAM "SPACERACE"

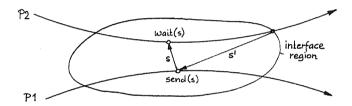

This program represents a system containing m identical processes which may be thought as being "vehicles" racing around on a plane according to their own laws (algorithms) of motion. Each of them is characterised by a position on that plane, represented by Cartesian coordinates, and a velocity. Another process drives the display device which shows the plane, i.e. its boundaries, and the m vehicles.

In order that these vehicles move on the screen "in real time", their coordinates are updated in discrete intervals of time called the update interval. We let this interval be (a multiple of) the clock pulse interval defined by the computer's line clock device (20 ms). A vehicle is thus described by a process of the form

### loop wait(tick); update coordinates end

This program differs from the previous program in several significant aspects:

- 1. There are many replicas (instances) of the same process pattern.

- 2. The interaction between the vehicles and the display driver is quite strong (all coordinates are shared interface variables), but it does not require mutual exclusion: the (refresh) display driver may easily access coordinates at the same time as a vehicle is updating them.

- 3. It is convenient to represent the coordinates x and y of vehicle i  $(1 \le i \le m)$  as elements of an array. Whereas each vehicle process i accesses x[i] and y[i] only, the display driver accesses x[k] and y[k] for all k. It is therefore impossible to represent these coordinates as simple variables of a distinct interface module. Fortunately, it is also unnecessary.

Let us first define the process which constitutes the behaviour of a vehicle. Each process is characterised by a position (x,y) and a velocity (dx,dy); dx is the amount by which x is incremented after each (real) time interval d dictated by the internal clock. In the same way dy is the increment of y. As soon as a vehicle hits the space boundary — we assume that the area is a rectangle adapted to the display screen — it bounces like a ball. This is represented by a sign inversion of the

appropriate velocity component. Let the elapsing of a time interval t be signalled by a tick, then the process may be formulated as follows:

```

process vehicle (i: integer);

begin (*assume x, y, dx, dy are initialised*)

loor wait(tick);

inc(x, dx);

if "x outside boundaries" then

dx := -dx; inc(x, dx) (*bounce*)

end:

inc(y, dy);

if "y outside boundaries" then

dy := -dy; inc(y, dy) (*bounce*)

end

end

end

end

```

The structure of the <u>display driver</u> (called "screen") is again a loop, expressing the repeated action of drawing the same picture (refreshing). We assume that the delay between two drawings is again given by the tick signal of the real time clock (it must be no more than 40 ms, because otherwise the screen starts to flicker).

The details of the statement "display picture of vehicle i" are determined by the peculiarities of the display processor GT 44. Explanation of the most important principles may suffice at this point; for further details the reader is referred to the manufacturer's manuals [6].

- The display processor is initiated by loading a storage address into the display program counter register (DPC). The processor then starts interpreting a sequence of instructions stored in consecutive locations starting at the given address.

- 2. There are so-called mode instructions which bring the processor into one of several modes for drawing lines, displaying text, or moving the beam to specified coordinates. Such coordinates are interspersed as data within the mode instructions, and are interpreted according to the set mode. (These data are absolute, there is no indexing. Hence the display processor is programmed like a very old-fashioned computer without index registers, conditional jumps, or subroutines. Our program exhibits this sorry state by listing display commands as octal numbers!)

- There exists a halt instruction which causes the main processor to be interrupted.

From these explanations it follows that a display code sequence

must be set up that defines the picture by which a vehicle shows up on the screen. We choose this to be a small square box enclosing a letter which identifies the vehicle (A ... H for m = 8), but shall not further describe the details of the display code sequences. It is important to note, however, that the coordinates of each vehicle must be inserted in the code before the display processor is initiated. Hence the statement "display picture of vehicle i" is expressed (refined) as follows:

```

fig[c1] := x[i]; fig[c2] := y[i];

fig[c3] := code for letter i;

DPC := adr(fig); doio

```

The "system" developed so far is not a very exciting one, because all vehicles move with fixed speed and fixed direction, which is only changed when the vehicle bounces at a screen (frame) boundary. We shall therefore seize the opportunity to introduce one more complication: speed and direction of the vehicle movements are to be made variable. Specifically, they shall be influenced by the interactive use of a light pen.

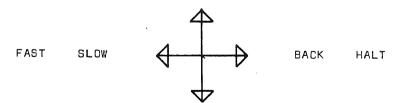

For this purpose, we postulate that n "commands" are to be displayed on the screen in addition to the vehicle (and the frame) themselves. Let us postulate the following n = 8 commands:

- 1. increase speed in the x-direction.

- 2. increase speed in the y-direction.

- 3. decrease speed in the x-direction.

- 4. decrease speed in the y-direction.

- 5. increase the update-interval (del)

- 6. decrease the update-interval

- 7. reverse the direction of movement

- 8. halt the vehicle at its current position.

We represent these commands by appropriate pictures in a (reserved) command area of the screen (see Fig 8).

Fig.8, Commands as displayed on screen

Of course, pointing to a command must affect a single vehicle only. Which one? We solve this identification problem by postulating that at all times one of the m vehicles be the "designated vehicle". It is designated by being spotted by the light pen. (Moreover, we shall ask that the letter identifying the designated vehicle be blinking. This is easily accomplished by an appropriate display instruction).

These considerations lead to the introduction of a variable z denoting the index of the designated vehicle. But how do we introduce the notion of the light pen seeing an item into our program? The solution is remarkably simple: the pen is represented by a <u>pen driver</u> process (called "pen"). The process waits for the pen catching sight by executing "doio". Therefore this process has once more a loop structure:

loop doio;

identify object seen and act accordingly

end

But how is the object seen identified? The hardware provides registers which hold the coordinates of the point being seen. But this facility is rather unheloful, because it requires an elaborate back-translation of coordinates to point or line or figure being identified. Therefore we ignore this facility and choose a much more effective solution. The identity of the currently drawn item (frame, figure, or command) is set and retained by the screen process in the form of two variables. mode" tells whether the frame, a figure, or a command is written (and therefore seen), and i tells which vehicle or command. These two variables therefore belong to the interface between the device processes "screen" and "pen", which are declared within the same device module. The first action after the pen has seen an object, is to determine the current mode. If it is "figure", the appropriate action is "z := i", because the seen vehicle becomes the designated vehicle. If the mode is command", then the designated vehicle's speed dx[z] or dy[z] or its update interval del[z] have to be changed appropriately (see orogram).

An inherent problem in the use of a light pen is that it has to be disabled temporarily after having spotted an item, because otherwise during the next refresh cycle it will see the same item again. The disabling must last an appropriate time to allow the withdrawal of the pen from the screen, whereupon it has to be reenabled. In the DEC GT-44 system, the pen is <u>not</u> disabled; instead, the entire display is stopped. It is up to the pen process to restart it. This action must include the explicit execution of a display processor instruction that disables interrupts due to the pen, because there is no status register with an interrupt enable bit. (In our example, this instruction included in the frame code.) This restart action of the screen within the pen process reveals that the current hardware is inappropriate to this method of structuring processes. The display device deviates in several respects unnecessarily from the comparatively regular and systematic handling of other devices, and in particular the light pen appears afterthought to the overall design. The present solution can at best be called an "elegant paint job", but it cannot hide the inherent incompatibility between the offered hardware and the systematic method of identifying devices as processes. Having executed the appropriate actions to interpret the seen command, and after having restarted the display processor, the pen process waits for an appropriate number of tick intervals, until it reenables the pen interrupts. The pen rests inoperative for about 0.5 sec.

Fig. 9 displays the resulting process structure of the entire system, and lists the respective interface variables and signals.

Fig.9. Processes, signals and shared variables

```

module spacerace;

const m = 8; (*no. of vehicles on screen*)

var i,xØ,yØ: integer;

scrsig, pensig: signal;

x, y: <a href="mailto:array">array</a> 1:m of integer; (*coordinates*)

dx, dy: array 1:m of integer; (*increments*)

del:

array 1:m of integer;

(*delay steps*)

device module display [4];

use x, y, dx, dy, del, pensig, scrsig, m;

const n = 8; (*no. of commands*)

var mode: (frame, figure, command);

i: integer:

z: integer; (*index of currently identified vehicle*)

dpc [1720008]: integer; (*display program counter*)

frm: <u>array 0:17 of</u> integer; (*frame display code*)

fig: array 0:13 of integer; (*vehicle display code*)

com: array 1:n, 0:15 of integer; (*command codes*)

process screen [3208]:

begin

loon wait(scrsig);

mode := frame; dpc := adr(frm); doio;

```

```

mode := figure; i := m;

receat fig[1] := x[i]; fig[2] := y[i]:

fig[11] := 64 + i:

if i = z then fig[10] := 1036308 (*blink on*)

else fig[10] := 1036200 (*blink off*)

end:

dpc := adr(fig): doio: dec(i)

until i = \emptyset:

mode := command: i := n:

reneat dpc := adr(com[i]); doio; dec(i)

until i = \emptyset

end

end screen ;

process pen [3248];

var d: integer:

begin

\frac{\text{loop}}{\text{frm[0]}} := 1171648; \text{ doio;} \quad (*\text{wait until pen signals*})

\text{frm[0]} := 1171258;

if mode = figure then z := i

elsif mode = command then

case i of

1: begin inc(dx[z]) end;

2: begin inc(dy[z]) end :

3: begin dec(dx[z]) end:

4: beain dec(dy[z]) end;

5: begin inc(del[z]) end;

6: begin dec(del[z]) end :

7: begin dx[z] := \emptyset; dy[z] := \emptyset; del[z] := \emptyset:

\underline{if} z = 1 \underline{then} halt(\emptyset) \underline{end}

8: begin dx[z] := -dx[z]; dy[z] := -dy[z] end :

end

end:

doc := adr(frm): (*restart display*)

d := 25:

repeat wait(pensig); dec(d) until d = \emptyset

end

end pen ;

begin (*display module; see note following this program*)

frm[ Ø] := 117124B; frm[ 1] :=

ØB: frm[ 2] :=

ØB:

frm[ 3] := 110000B; frm[ 4] := 041777B; frm[ 5] :=

frm[ 6] := Ø4ØØØØB; frm[ 7] := ØØ1777B; frm[ 8] := Ø61777B; frm[ 9] := ØB; frm[10] := Ø4ØØØØB; frm[11] := Ø21777B;

ØB; frm[10] := 040000B; frm[11] := 021777B;

frm[12] :=

\emptyset B: frm[13] := \emptyset \emptyset \emptyset 2 \emptyset \emptyset B; frm[14] := \emptyset 41777B;

frm[15] :=

\emptyset B: frm[16] := 1734\emptyset B:

fig[ 0] := 117024B; fig[ 1] := 0B; fig[ 2] := 0B; fig[ 3] := 104000B; fig[ 4] := 050000B; fig[ 5] := 040040B;

fig[ 6] := 070000B: fig[ 7] := 040140B: fig[ 8] := 130000B:

fig[ 9] := 002206B; fig[10] := 103620B; fig[11] :=

ØB:

fig[12] := 173400B:

com[1,\emptyset] := 117\emptyset24B; com[1,1] := \emptyset01000B; com[1,2] := \emptyset00100B;

com[1,3] := 104000B; com[1,4] := 056000B; com[1,5] := 062010B;

com[1,6] := \emptyset4\emptyset12\emptysetB; com[1,7] := \emptyset42\emptyset1\emptysetB; com[1,8] := 1734000B;

com[2,0] := 1170248; com[2,1] := 0010008; com[2,2] := 0001008;

com[2,3] := 104000B; com[2,4] := 040070B; com[2,5] := 062110B;

```

```

com[2,6] := \emptyset44\emptyset\emptyset\emptysetB; com[2,7] := \emptyset62\emptyset1\emptysetB; com[2,8] := 1734\emptyset\emptysetB;

com[3,\emptyset] := 117024B; com[3,1] := 001000B; com[3,2] := 000100B;

com[3,3] := 104000B: com[3,4] := 076000B: com[3,5] := 042010B:

com[3,6] := \emptyset4\emptyset12\emptysetB; com[3,7] := \emptyset62\emptyset1\emptysetB; com[3,8] := 1734\emptyset\emptysetB; com[4,0] := 117024B; com[4,1] := 001000B; com[4,2] := 0001000B;

com[4,3] := 104000B: com[4,4] := 040170B: com[4,5] := 062010B:

com[4,6] := \emptyset44\emptyset\emptyset\emptysetB; com[4,7] := \emptyset6211\emptysetB; com[4,8] := 17340\emptysetB;

com[5,0] := 117620B; com[5,1] :=

300B; com[5,2] :=

com[5,3] := 1000000B; com[5,4] := 046123B; com[5,5] := 053517B;

com[5,6] := 173400B:

com[6,\emptyset] := 11762\emptysetB; com[6,1] :=

500B: com[6,2] :=

70B:

com[6,3] := 1000000B: com[6,4] := 040506B: com[6,5] := 052123B:

com[6,6] := 173400B:

com[7,0] := 117620B; com[7,1] := 1200B; com[7,2] :=

com[7,3] := 1000000B; com[7,4] := 040510B; com[7,5] := 052114B;

com[7,6] := 173400B:

com[8,0] := 117620B; com[8,1] := 1500B; com[8,2] :=

com[8,3] := 1000000B; com[8,4] := 040502B; com[8,5] := 045503B;

com[8,6] := 173400B;

mode := frame: z := 1: screen: pen

end display:

device module timing [6]:

define tick:

var tick: signal:

lcs [177546B]: bits:

process clock [1008]:

begin lcs[6] := true:

loop doio:

while awaited(tick) do send(tick) end

end

end clock:

begin clock

end timina :

process vehicle(i: integer);

var d: integer:

begin

<u>loop</u> d := del[i]:

repeat wait(tick); dec(d)

until d < Ø:

inc(x[i], dx[i]);

if(x[i] < \emptyset) or (x[i] > 1740B) then

dx[i] := -dx[i]; inc(x[i], dx[i])

end :

inc(y[i], dy[i]);

if(y[i] < 2008) or(y[i] > 17408) then

dy[i] := -dy[i]; inc(y[i], dy[i])

end

end

end item ;

process clock:

begin

loop wait(tick): send(scrsig): send(pensig)

```

```

end

end clock;

begin (*spacerace*) i := m;

xØ := 2000B/(m+1); yØ := 220B;

reneat x[i] := i*xØ; y[i] := yØ;

dx[i] := Ø; dy[i] := Ø; del[i] := Ø;

vehicle(i); dec(i)

until i = Ø;

clock

end spacerace .

```

The arrays frm, fig, and com represent the code for the GT-44 display processor. Its "language" is not part of Modula, and the commands are therefore denoted by octal numbers [6]. The following alternative specifications (for frm and fig only) should convey an idea of the nature of this code.

```

picture frm: (*frame*)

begin point[intensity 4, blink off, solid lines](0,0);

longvector(L,0)(0,L)(-L,0)(0,-L)(0,128)(L,0)

end frm:

picture fig(x,y: integer; z: char); (*vehicle*)

begin point[intensity 4, blink off, solid lines](x,y);

shortvector(D,0)(0,D)(-D,0)(0,-D);

relativepoint(9,6);

character[intensity 7, blink on] z

end fig

```

L = 1023 is the frame width, and D = 32 is the width of the square depicting a vehicle.

#### References

- N.Wirth, "Modula: A language for modular multiprogramming", Institut für Informatik, Report 18, ETH Zürich, March 1976.

- E.W.Dijkstra, "Cooperating sequential processes", in Programming Languages, F.Genuys, ed., Acad. Press, London 1968.

- R.G.Nordman, R.L.Smith, L.A.Witkin, "New CRT terminal has magnetic tape storage for expanded capability", Hewlett-Packard Journal 27, 9, 2-15 (May 1976).

- 4. 2644A Mini Data Station, owner's manual, Hewlett Packard manual No. 02644-90001 (Nov.1975).

- 5. C.A.R.Hoare, "Monitors: An operating system structuring concept", Comm.ACM 17, 10, 549-557 (Oct.1974).

- GT-44 user's guide. Digital Equipment Corp. DEC-11-HGT44-A-D.

- 7. N.Wirth, "Design and implementation of Modula", in this Report.

,

## DESIGN AND IMPLEMENTATION OF MODULA

N.Wirth

### Abstract

This paper gives an account of some design decisions made during the development of the programming language Modula. It explains the essential characteristics of its implementation on the PDP-11 computer, in particular its run-time administration of processes and the mechanism of signalling. The paper ends with some comments on the suitability of the PDP-11 for this high-level multiprogramming language.

Author's address: Institut für Informatik, ETH, CH-8092 Zürich

# DESIGN AND IMPLEMENTATION OF MODULA

#### 1. Introduction

In this report I shall try to do two things: to give an account of how and why certain design decisions were made in the development of the programming language Modula, and to explain some details of its implementation on the PDP-11 computer. The reader is referred to the defining report of Modula [1] which also contains a brief overview of the language, and to the companion paper illustrating some typical applications of Modula [2].

The entire project started out with the modest aim to gain some experience and insight in the field of multiprogramming and device handling. Such insight, it was stipulated, could well lead to a set of practical rules or guidelines for effective and reliable multiprogram system design, that could ultimately consolidate into a discipline. It soon became evident that the creation of such a set of rules amounted to nothing less than the design of a new "language", i.e. a set of notations and structures in terms of which design would proceed. Some programs were developed in this way and formulated in assembly code. This approach made it possible to experiment whith some proposed elements on which the design discipline was to evolve, but more significantly it also drove home a message that actually should have been known already: that the mere proposal of an abstract notational scheme to design systems (which thereafter must be coded by hand in a low-level language) will neither lead to reliable products nor to a significant saving in development cost. The necessity of a high-level language with a fully automated compilation process is unquestionable. The modest learning effort in multiprogramming thus slowly evolved into another exercise in language design and implementation.

Our desire to take over many familiar elements from Pascal is understandable. After all, our aim was to concentrate on the novel aspects due to multiprogramming, and not on the design of an entirely new language in toto. Yet, the occasion was seized to change several details, and in particular to omit certain facilities that are either complicated to implement, or not needed in the context of our original goal, or both. In retrospect, Modula turned out to be a language considerably smaller than Pascal. Yet it provides ample room for experimenting and exploring good techniques of programming, for committing blunders and recognising that multiprogramming is truly difficult even with a neat and systematic tool at hand.

The development of the compiler was started when a sketchy definition of the language had been laid out. The compiler was written in Pascal as a one-pass cross-compiler running on the CDC 6400. This approach allowed a relatively quick adaptation to language specification changes, which were rather frequent for a considerable time. Yet the exercise proved once again that, unless a very large part of the language is "right" at the beginning, such a project has a small chance to survive. It is

particularly important to choose the right moment when a language definition is to be stabilized, i.e. when a report is to be released for programmers, and when a second effort is to be launched aiming at a well-engineered, efficient compiler.

This paper discusses a few selected topics only, in particular those that distinguish Modula from Pascal. These are the module structure and all facilities concerned with concurrent processes. The discussion of aspects of implementation is restricted to the run-time organization; we refrain from commenting on compiler technology.

### 2. Modules

The block structure of Algol and Pascal with its facility to declare local objects does not adequately cover the needs of systems programming. In particular, it does not allow to hide objects (or details about them), while they are still in existence. Objects cease to exist, as soon as control leaves the procedure (block) to which they are local. To some degree, the own variables of Algol 60 incorporate the desired information hiding property. However, the own concept has well-known deficiencies, and a different solution has to be found.

A very much more appropriate solution was offered by the <u>class</u> concept of Simula as modified by Brinch Hansen and Hoare [3,4,5]. The class definition defines a set of procedures (operators) and a set of variables to which only these procedures have access. The important aspect is that these variables continue to exist, if control leaves any of these procedures.

Why then, did we not adopt the class structure in Modula? The primary reason is that the unit of program which encapsulate information from its environment - now called a module - appears to be of relatively large size in systems programming, and that usually only one instance of such a module exists. This is in contrast to the original aim of the class concept, where there exist many such objects of identical structure. They form a class . The class embodies the idea of an abstract data type to be declared in conjunction with its applicable operators [6,7]. The module, however, rather pursues the aim of an adequate facility to declare such entities as, for example, a scanner in a compiler, a disk store manager in an operating system, or a communication line handler in a data station. Hence, the module has somewhat different objectives than the class, and it would therefore be misleading to claim that the module concept replaces the class concept, although it can be shown that formally the former covers the latter. We shall show how a class definition can be represented by a module declaration, and then discuss the advantages and disadvantages of the two structures.

Consider the following class definition [4]:

This is expressed in terms of a module as follows:

```

module M:

define R,q,s:

type R = record x,y: T end;

procedure p(yar r: R; U);

begin ... end p;

procedure q(yar r: R; V);

begin ... end q;

procedure s(yar r: R);

begin S

end:

```

The advantage of the class is evident, if we create several instances of the data structure, each consisting of the two components x and y:

```

var a,b: C

```

Thereby the initialization statement S is implicitly invoked once for a and once for b. An invokation of procedure q, applied to a is expressed conveniently as

```

a.q(v)

```

where a appears as a parameter in a distinguished position. In the case of the module structure, the two variables are declared as

var a,b: R

and the call as

q(a,v)

Initialization must be stated explicitly as s(a). The principal advantage of the class notation appears, if there are several classes, perhaps with the same identifiers for some of their individual operators: their names are entirely local, and their identity is determined by the prefixed parameter, whose type uniquely specifies one class.

It is not our intention to belittle these advantages, but the sophisticated combination of using a distinguished parameter position to identify the scope in which its operator is defined

is of much lesser importance in the application area envisaged for modules. It seems only natural that the designer of a system chooses unique names for all operators exported from different (parallel, not nested) modules. The primary advantage is then one of conceptual simplification: the module has one and only one function, namely to establish a static scope of identifiers, whose acrossboundary visibility of identifiers is strictly under the programmer's control. Export (and import) rules are not restricted to some operators (procedures), but apply identically to names of any kind of object, such as constants, types, variables. This generality of scope rules has in practice proved to be highly valuable.

If only one instance of a class variable is to appear, then of course the module notation is equally simple, if not simpler. The declaration

module M; define q; var x,y: T; orocedure q(V);

. . . .

<u>beain</u> S end M

replaces both the class definition and its instantiation a:C, and the call q(v) replaces a.q(v). In the case of multiple instances the module notation is more cumbersome, but also provides some additional possibilities, such as, for example, the introduction of variables common to all class instance operators declared in the module heading and initalised in its body.

Implementation of the module is, considering the additional possibilities, simpler than that of the class. After all, the only conceptual innovation of the module lies in delimiting the scope of identifiers. In the compiled code, there appears no trace of the module structure itself. Nevertheless, the additional sophistication of the compiler's symbol table mechanism is rather considerable, and in any case greater than anticipated. It weighs particularly in the case of multipass compilers. Unfortunately, it appears to be almost impossible to avoid a multi-pass scheme. This not only in view of Modula's application to minicomputers with limited store size, but primarily because of the potential desirability of cross references of objects defined in different modules.

There are two issues that gave rise to some discussions: the read-only nature of exported variables, and the intransparency of exported types. The latter stems from the desire to match the class definition's power of internal structure hiding. Hence, a programmer using an exported type (e.g. R in the above example) cannot use any knowledge about the details of R, not even does he "know", for example whether R is a record or an array structure.

The decision to declare every exported variable to be a readonly variable is based on the view that variables belonging to a module actually should not be exported at all. Making them exportable as read-only variables, however, avoids the cumbersome declaration of function procedures that merely yield a variable's value.

#### 3. General Processes

The most important and predominant decisions to be taken in the design of a multiprogramming language implementation are those concerning storage allocation and processor management (scheduling). The guiding criteria in the decisions taken here were efficiency and simplicity of addressing (of variables) and of signalling operations. The latter are the only programmed operators that may cause the processor to switch from one process to another. Another objective was a minimal run-time support routine.

# 3.1. Storage layout

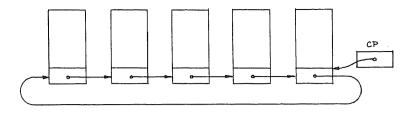

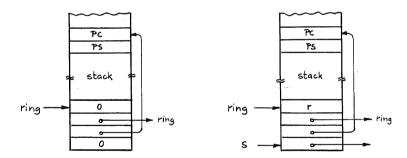

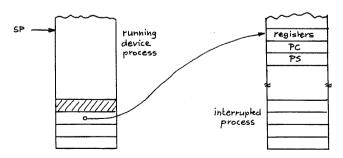

language Modula projects a view of systems consisting of a fixed number of concurrently active processes. This concept eliminates the need for a dynamic storage management scheme among processes. But even for primitive systems, this view of an entirely static world is somewhat too simplicistic: even simple systems, upon "deadstart", grow from an initial nucleus to their operating" complexity. Modula therefore supports the possibility of dynamic process generation (and allocation of their workspace). However, it does not support the notion of their dissolution. (In fact, a process may terminate, but this does not imply the recycling of its store). Modula restricts the ability to generate new processes to the main program part. This brings two advantages. First, all complications arising from processes having "sons" (which perhaps survive their ancestors) are avoided. Second, after the main program has reached a specific point (usually the end), it is guaranteed that no storage overflow can occur. This is crucial in all process control systems, where the main program part assumes the role of an initialization phase. During this phase, storage is allocated sequentially as needed by newly generated processes. Each data segment contains a header containing a link to another process. All processes are thus linked in a single ring. This header, called the process descriptor also represents the state of the process when it is not being served by the processor.

Fig.1. Workspaces of processes linked in a ring.

Naturally, each process has its own stack (work space). Each stack is of fixed size. This size may be computed by the compiler, provided that no procedure is activated recursively. Modula, however, does allow recursion. In this case, a compiler directive must indicate the maximum depth of the recursion.

# 3.2. Addressing\_of\_variables